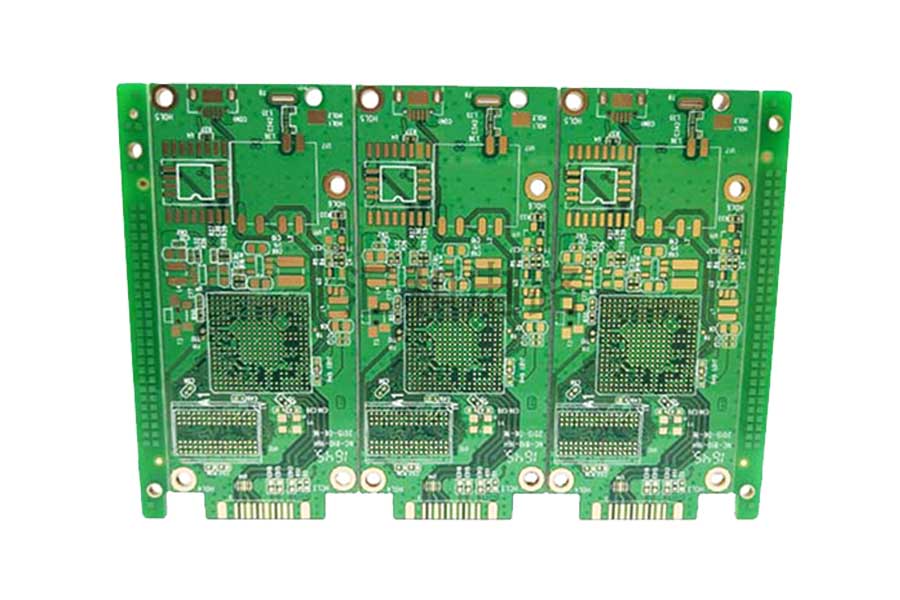

8 ലെയർ HASL PCB

എന്തുകൊണ്ടാണ് മൾട്ടി ലെയർ പിസിബി ബോർഡുകൾ കൂടുതലും തുല്യമായിരിക്കുന്നത്?

ഇടത്തരം, ഫോയിൽ പാളികളുടെ അഭാവം കാരണം, ഒറ്റ പിസിബിക്കുള്ള അസംസ്കൃത വസ്തുക്കളുടെ വില പിസിബിയേക്കാൾ അല്പം കുറവാണ്.എന്നിരുന്നാലും, ഒറ്റ ലെയർ പിസിബിയുടെ പ്രോസസ്സിംഗ് ചെലവ് ഇരട്ട ലെയർ പിസിബിയേക്കാൾ വളരെ കൂടുതലാണ്.ആന്തരിക പാളിയുടെ പ്രോസസ്സിംഗ് ചെലവ് ഒന്നുതന്നെയാണ്, എന്നാൽ ഫോയിൽ/കോർ ഘടന ബാഹ്യ പാളിയുടെ പ്രോസസ്സിംഗ് ചെലവ് ഗണ്യമായി വർദ്ധിപ്പിക്കുന്നു.

കോർ സ്ട്രക്ചർ പ്രോസസിന്റെ അടിസ്ഥാനത്തിൽ നോൺ-സ്റ്റാൻഡേർഡ് ലാമിനേഷൻ കോർ ലെയർ ബോണ്ടിംഗ് പ്രോസസ്സ് ഓഡ് ലെയർ പിസിബിക്ക് ചേർക്കേണ്ടതുണ്ട്.ന്യൂക്ലിയർ ഘടനയുമായി താരതമ്യപ്പെടുത്തുമ്പോൾ, ആണവഘടനയ്ക്ക് പുറത്ത് ഫോയിൽ കോട്ടിംഗ് ഉള്ള പ്ലാന്റിന്റെ ഉൽപാദനക്ഷമത കുറയും.ലാമിനേഷനു മുമ്പ്, പുറം കാമ്പിന് അധിക പ്രോസസ്സിംഗ് ആവശ്യമാണ്, ഇത് പുറം പാളിയിലെ പോറലുകൾക്കും എച്ചിംഗ് പിശകുകൾക്കും സാധ്യത വർദ്ധിപ്പിക്കുന്നു.

വൈവിധ്യമാർന്ന പിസിബി പ്രക്രിയകൾ

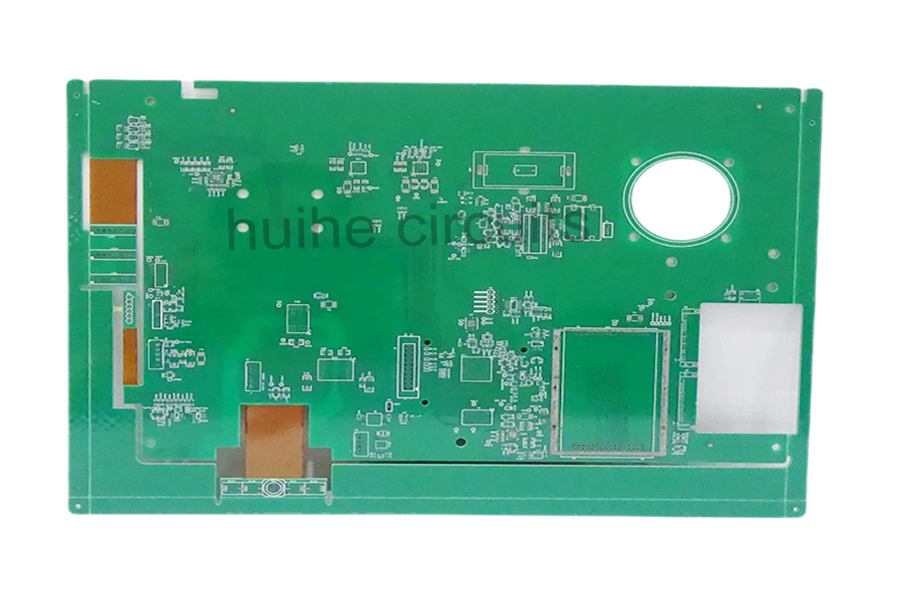

റിജിഡ്-ഫ്ലെക്സ് പിസിബി

വഴക്കമുള്ളതും നേർത്തതും, ഉൽപ്പന്ന അസംബ്ലി പ്രക്രിയ ലളിതമാക്കുന്നു

കണക്ടറുകൾ കുറയ്ക്കുക, ഉയർന്ന ലൈൻ വഹിക്കാനുള്ള ശേഷി

ഇമേജ് സിസ്റ്റത്തിലും RF ആശയവിനിമയ ഉപകരണങ്ങളിലും ഉപയോഗിക്കുന്നു

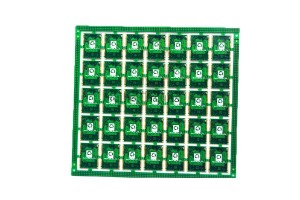

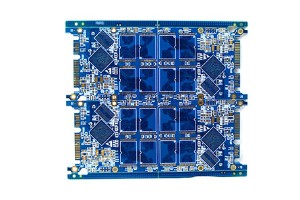

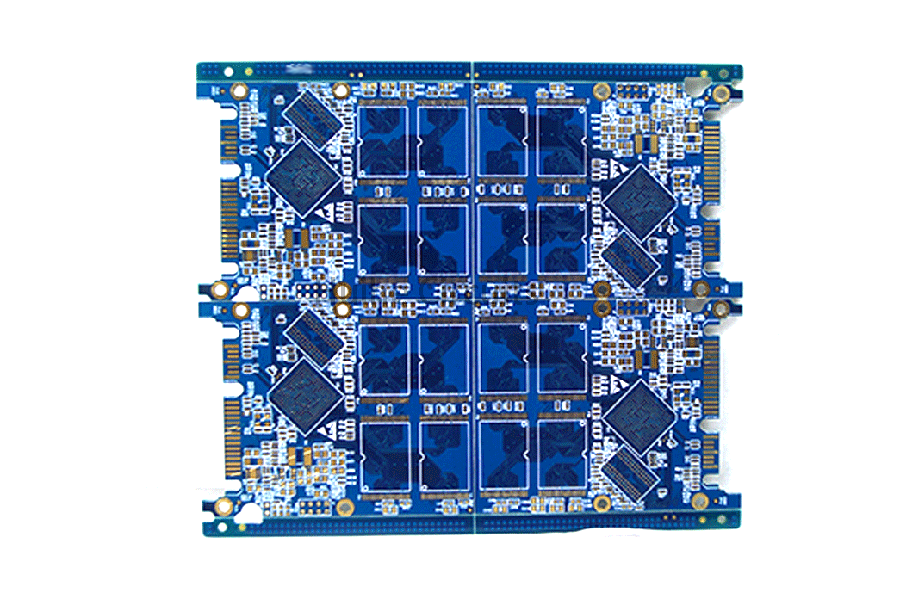

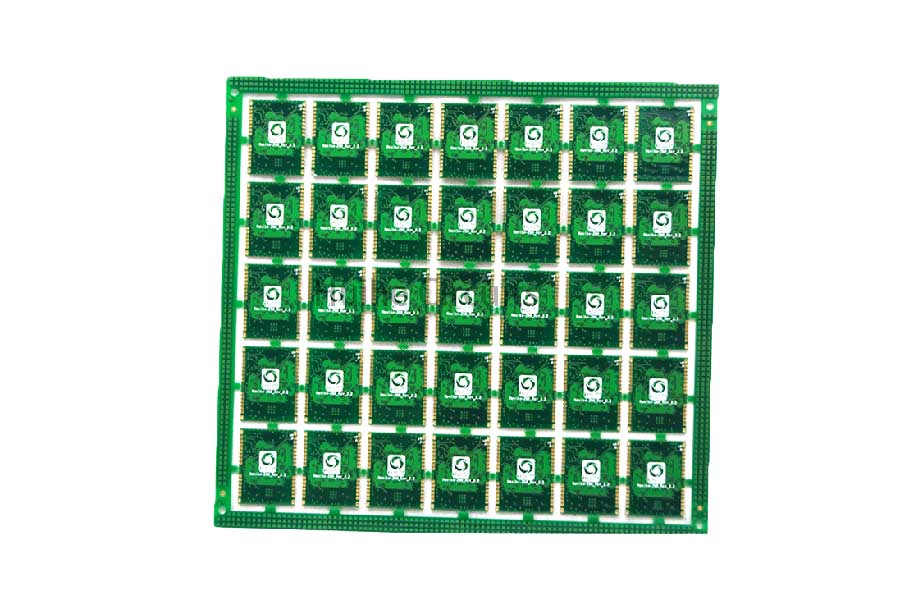

മൾട്ടിലെയർ പിസിബി

ഏറ്റവും കുറഞ്ഞ ലൈൻ വീതിയും ലൈൻ സ്പെയ്സിംഗും 3/3മി

BGA 0.4പിച്ച്, ഏറ്റവും കുറഞ്ഞ ദ്വാരം 0.1mm

വ്യാവസായിക നിയന്ത്രണത്തിലും ഉപഭോക്തൃ ഇലക്ട്രോണിക്സിലും ഉപയോഗിക്കുന്നു

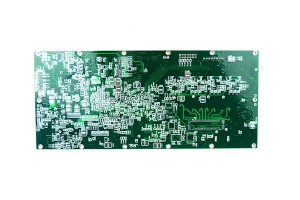

ഇംപെഡൻസ് കൺട്രോൾ പിസിബി

കണ്ടക്ടർ വീതി / കനം, ഇടത്തരം കനം എന്നിവ കർശനമായി നിയന്ത്രിക്കുക

ഇംപെഡൻസ് ലൈൻവിഡ്ത്ത് ടോളറൻസ് ≤± 5%, നല്ല ഇംപെഡൻസ് പൊരുത്തപ്പെടുത്തൽ

ഹൈ-ഫ്രീക്വൻസി, ഹൈ-സ്പീഡ് ഉപകരണങ്ങൾക്കും 5g ആശയവിനിമയ ഉപകരണങ്ങൾക്കും ബാധകമാണ്

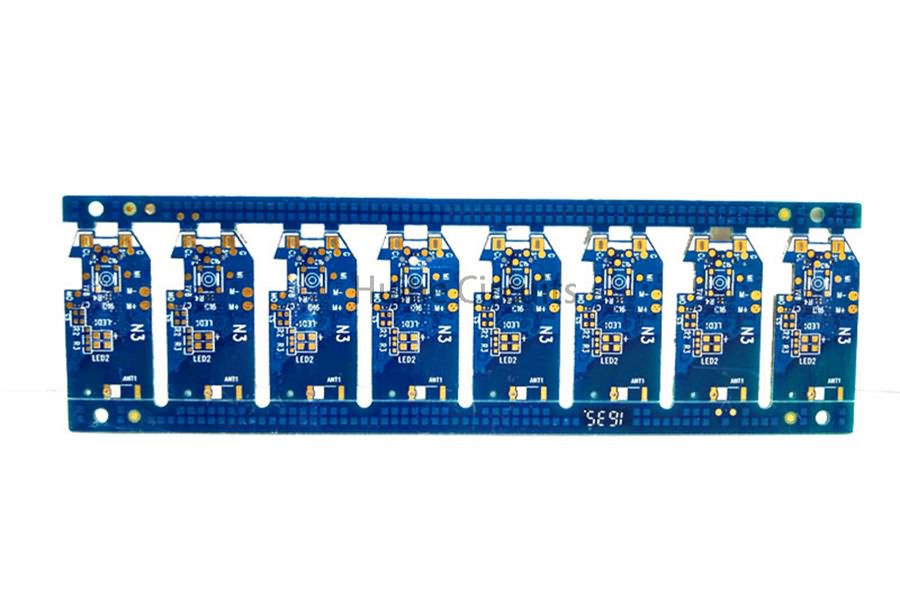

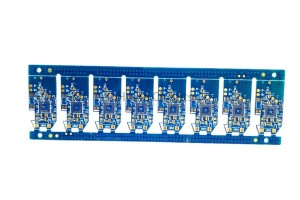

ഹാഫ് ഹോൾ പിസിബി

പകുതി ദ്വാരത്തിൽ ചെമ്പ് മുള്ളിന്റെ അവശിഷ്ടമോ വേർപിരിയലോ ഇല്ല

മദർ ബോർഡിന്റെ ചൈൽഡ് ബോർഡ് കണക്റ്ററുകളും സ്ഥലവും ലാഭിക്കുന്നു

ബ്ലൂടൂത്ത് മൊഡ്യൂളിലേക്ക് പ്രയോഗിച്ചു, സിഗ്നൽ റിസീവർ